车载计算机的研究与设计

庄凌昀 谢维达

(同济大学铁道与城市轨道交通研究院,201804,上海∥第一作者,硕士研究生)

铁路与城市轨道交通的列车运行环境可能是高低温、高湿、冲击、电磁辐射干扰、振动等恶劣环境,因此,列车控制系统中微机系统的可靠性非常重要。研究表明,考虑到当前传统微机系统结构,仅仅从目前元器件的工艺技术水平出发,暂无有效的办法提高微机系统整体的可靠性。因此,应立足于列车微机控制系统,参考国内外经验,特别是冗余容错计算机,采用高可靠性多冗余容错技术,研究与设计车载计算机系统,以满足列车控制中可靠性安全性要求[1]。

1 车载计算机安全性分析、设计与应用

不同于安全继电器组成的铁路信号设备,车载计算机主要由微机及超大规模集成电路芯片组成,因此不具备非对称故障特性。车载计算机安全性设计主要是依据可靠性理论和容错技术。通过软件和硬件冗余容错设计以及移植实时操作系统,有效提高微机控制系统可靠性,进而提高列车运行的安全性;充分发挥计算机高速、智能处理能力,设计完善的软、硬件故障检测模块,确保控制系统芯片正常运行,程序准确执行,列车各个设备接收和执行正确无误的指令。

车载计算机是列车微机控制系统的主要核心部件。整个车辆控制系统中,为了满足不同应用要求和系统安全性及可靠性需求,将微机控制系统中一些关键部件由传统单芯片微机改为高可靠性安全性、具有冗余容错的车载计算机部件。

例如CCU(中央控制单元)负责列车通信网络,TCU(牵引控制单元)负责控制牵引变流器和牵引电机,BCU(制动控制单元)负责列车制动等。由于这些控制单元在列车运行中至关重要,直接影响到行车安全,因而对其可靠性要求尤为严格。目前工程设计中常采用系统级双机热备冗余或一热备一冷备冗余。如何设计出通用的高可靠性车载计算机控制单元,通过冗余措施确保对外运行安全性,并保留输入输出端口通用性,且能够适应列车微机控制系统的不同应用要求,具有较好硬件兼容性以及应用扩展性,设计与研究高可靠、高可用、高安全车载安全计算机的要求。它对于保证与提高整个列车微机控制系统可靠运行是十分有意义的。

本文研究与设计的车载计算机,主要针对基于嵌入式单片机芯片处理器、利用高主频运算速度、大容量存储单元、集成多种通用总线以及A/D,D/A转换接口等特点,根据实际需要,移植实时操纵系统以及编写相应的上层应用软件,或者通过扩展外围电路满足特殊实际要求。微机单元运行中,需要对大量数据进行运算处理的控制单元。这一类计算机已应用在大量信息处理、网络通信控制、任务进程调度、故障诊断与终端显示等场合,在列车微机控制系统中处于重要地位,决定着整个控制系统的可靠性与安全性。

2 系统组成及工作原理

整个系统主要由3个CPU和FPGA(现场可编程的阵列)构成的FIFO(先入先出)模块以及表决器组成。从系统结构图可以看出,不仅对 CPU模块进行冗余,而且信号缓冲、输出接口都冗余设计。实际应用中,CPU模块可以根据技术需要选择X86、PC104系统,也可选择ARM,DSP等其他微机芯片设备。

车载计算机的工作原理如图1所示。3个独立的CPU单元通过数据采样设备获取数据,进行处理后分别输出至各自对应FPGA的 FIFO模块;FPGA将得到的数据以先入先出的模式传送至表决器,进行3取2表决,得到正确数据。表决器确定一个正确工作的CPU,将控制信号传输至输出控制单元。表决器应当保证此时有且仅有一个输出控制单元工作,使得正确工作的CPU将运算结果通过输出转换单元传至外部设备。

图1 车载计算机结构框图

车载计算机冗余模式可以考虑 TMR(三模冗余),通过表决器获得正确结果。考虑到车载计算机应用的通用性,CPU模块宜选用ARM芯片。

3 冗余模式的选择

冗余方式主要有双模冗余、三模冗余、N模冗余等。考虑到实际运用中的可靠性,无论是双机一冷备一热备还是双机热备,都比三模冗余表决系统的可靠性高。通过分析,三模冗余表决系统的最大优点在于故障判断和切换时输出连续不中断,信息数据可以持续输出。双模冗余采用比较方式,三模冗余采用多数表决(3取2)。一旦系统发生错误,双模冗余不能对故障进行判断和定位,不能保证输出结果正确性。三模冗余可确保一个单元发生错误时,整个系统仍能保证有正确的数据输出,并准确地判断和定位发生故障的单元。通过容错管理软件控制,可根据实际需要将三模冗余降到双模冗余,再根据需要从双模冗余降到单模运行,从而确保了在一个CPU模块发生故障时整个系统依旧可以正常工作、两个CPU模块发生故障仍可以确保系统安全运行。整个系统根据“故障-安全-故障-运行”的工作思想进行设计系统的冗余工作方式。

4 表决器设计

表决器设计时主要包括输入和输出两部分。输入接口设计成FIFO结构,每个CPU模块分别将经过处理的数据输入FPGA多数表决。表决器可用FPGA逻辑单元构成,根据表决结果,输出一个统一开关控制信号,分别输至3个CPU模块各自对应的输出控制单元。输出控制单元根据控制信号进行判断,决定最终向外输出的CPU模块。每次仅有一个CPU模块向外界设备输出运算结果。

这里采用FIFO,因为它既能保证信息交换传输的高速率,又可以有效地避免芯片系统布线。特别在FPGA中,可以方便地构造多个FIFO及其逻辑组合。双口RAM结构存储器需要系统总线提供足够多的数据线、地址线、命令线和控制线,也存在占用接点过多的问题。在研究与设计中,应综合比较考虑两者特点。

由于输出部分表决判断3个CPU模块的运行结果,理论上3个完全相同的CPU模块加载运行相同的程序,当同一个信号数据输入时,应当输出相同的运算结果。假设单独一块CPU模块因工作环境干扰导致死机或程序跑飞,必有一个错误的信号或数据输出。通过3取2表决三模冗余,可以屏蔽错误信号,得到一个正确的结果。表决器通过表决,将正确运行的CPU接通对外设备输出,并可以根据各个CPU发生错误的累计次数,将故障的CPU切断脱离工作状态,重新上电恢复工作。

由于表决器是单独电子设备,因而决定了整个系统的可靠性,设计时对表决设备进行旁路设计。表决器本身可以自检。如果表决器出现短暂输出错误(如不能同时选择2个CPU模块或者3个CPU模块对外输出),或是表决器无法正常实现表决工作,则通过默认配置,将之前系统连续正确工作的CPU作为对外输出的单元构成单模系统,或依次对外单独工作;也可以考虑将表决器进行三模冗余,提高整个系统的可靠性。

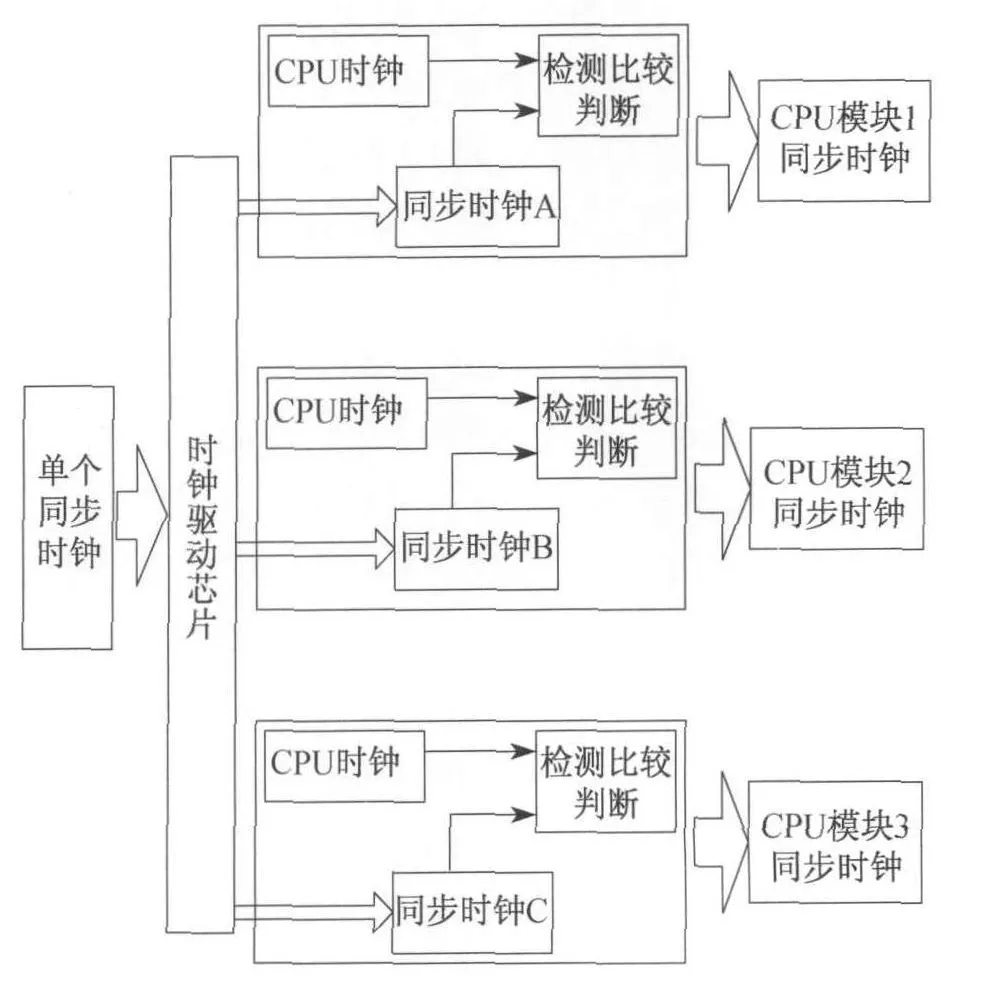

5 同步设计

在三模冗余系统中,时钟同步信号直接影响整个系统效率。不同步的时钟信号直接导致各个CPU处理数据结果也不同步,表决器得到错误数据,冗余系统没有意义。工程应用中通过软件同步以及硬件同步来实现时钟同步的功能。软件同步通常应用于通信系统。事实上,由于芯片间批量数据高速通信,各个模块之间大量数据交换,软件同步大多较难满足要求,因此采用硬件同步为满足实时性要求。硬件同步方法可以达到纳秒级的同步精度,这是软件通信同步无法达到的精度。工程中常用的硬件同步方法如下:

(1)公共时钟信号——所有CPU模块采用同一时钟信号。此方法简单并且可以保证时钟信号同步精确度。由于采用了同一时钟信号,公共时钟发生故障后很容易引起全部时钟信号错误。

(2)精确独立时钟信号——各CPU模块采用独立时钟,理论上保证足够精确就可保证各个时钟信号同步。实际上,各个独立的时钟信号在输出频率之间一定会存在细微差异;当差异逐渐积累,最终导致时钟不同步,表决器无法正常工作。

(3)互反馈独立时钟信号——各CPU模块采用独立时钟信号,各时钟之间互反馈调节达到同步功能。此方法硬件设计复杂,但可以提供长时间外部没有参考的冗余容错时钟信号。

3个CPU模块采用各自独立时钟,但用同一个时钟(同步时钟)基准进行同步控制。为提高同步时钟可靠性,由CPU模块上的时钟对同步时钟进行检测。如果检测时钟正常则采用同步时钟,如果检测发现时钟错误则切换到CPU时钟。此时,3个CPU单元如果无法实现同步,必须降模运行,其余作为冷备运行。

图2是同步时钟检测电路的设计。该部分选择FPGA来实现硬件电路。作为一种集成了众多的逻辑单元芯片,FPGA内部可以根据实际需要对逻辑门进行软件分配,构造实际需要的各种门电路,并且体积小、灵活性高、处理速度快。关键在于与传统分立元件不同有较高的可靠性。

图2 同步时钟检测电路

6 软件设计

传统列车微机控制系统中设计编写的应用软件,往往是针对不同的微机平台和功能。这样设计的好处在于应用软件具有灵活的操作性适用性,缺点是整个应用程序的可靠性完全依赖设计人员的专业水平。微机以及程序在工作时发生死机现象以及程序跑飞的情况与应用软件直接相关。

通过在列车车载计算机CPU模块芯片单元内移植VxWorks实时操作系统,根据不同的应用场合,编写移植相对应的应用程序。VxWorks是美国WIND RIVER风河公司推出的操作系统,在众多对于强调安全的工程项目,诸如卫星系统,战斗机控制系统等有着广泛的工程实际应用。列车控制系统上移植与应用实时操作系统是微机控制系统发展的方向与趋势。其原因是:首先,整个系统的可靠性由实时操作系统保证,避免了单独片上程序运行中死机问题;其次,可以根据车载计算机在不同场合的需要,裁剪相应的系统操作部件;最后,VxWorks在列车信号控制系统等其他方面已经有较广泛的应用。

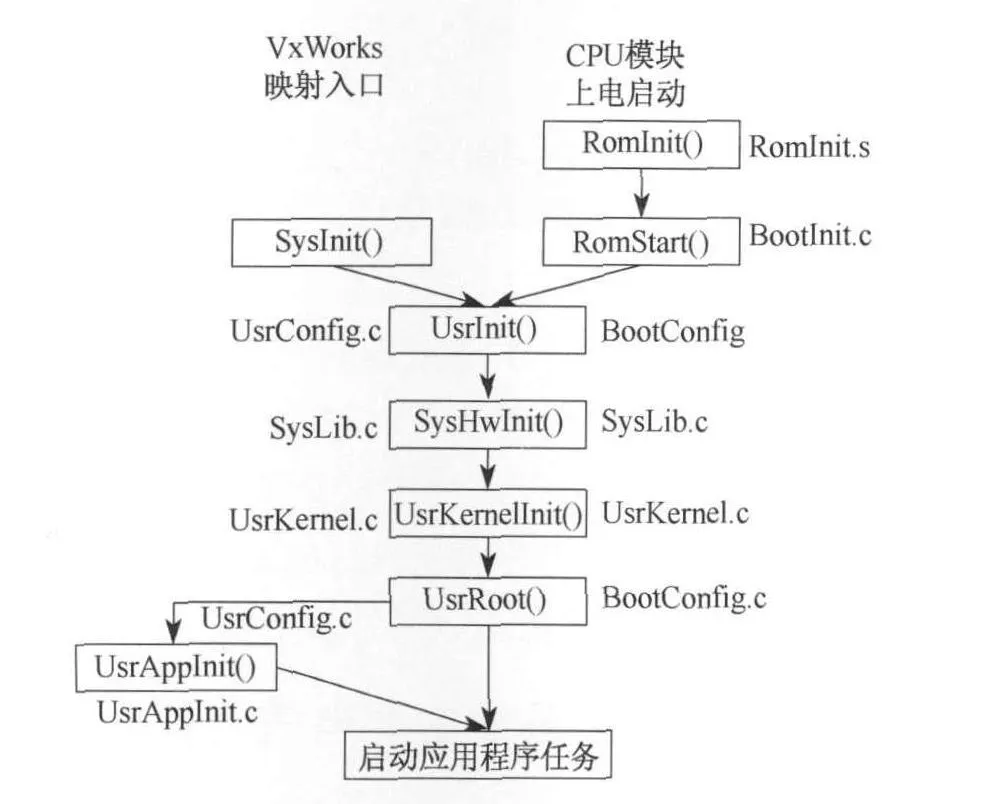

整个车载计算机CPU模块VxWorks系统启动流程如图3所示。

图3 VxWorks系统启动流程

VxWorks系统启动分为两个阶段。

第一阶段流程如图3右侧:首先执行 RomInit(),主要完成的任务包括禁止中断、保存启动类型(冷/热启动)和硬件相关初始化;然后调用RomStart(),主要完成将BootRom的数据段和代码段从ROM复制到RAM中,并清空内存;随后调用UsrInit(),执行系统初始化程序;最后执行SysHwInit()和kernelInit(),初始化系统硬件并启动内核,清空缓存。至此,BootRom阶段启动结束。

第二阶段流程如图3左侧图示进行VxWorks系统映像:通过第一阶段加载的BootRom引导映像,将VxWorks映像装入到RAM中,跳转到VxWorks映射入口;调用SysInit(),完成包括锁住中断、禁用缓冲、初始化处理器得到一个缺省值、指明启动类型等任务;系统再依次调用 UsrInit(),SysHwInit()和KernelInit();硬件和内核完成初始化后,系统执行UsrRoot()。该程序主要完成初始化I/O操作系统、安装设备驱动程序、创建设备等任务。最后启动应用程序。车载计算机的设备驱动特定,并不需要创建其他设备,所以这些步骤在UsrRoot()函数中能完成,并最后启动应用程序[3]。

上述采用BootRom+VxWorks的启动方式多用于车载计算机研究设计以及调试阶段,程序映像即可存放在硬盘中,也可通过网络加载。采用这种启动方式的优点是适应硬件、方便调试和现场升级,并且由于设计了BootRom,整个设计也考虑到CPU模块的兼容性。通过研究与移植实时操作系统,可提高车载计算机可靠性与安全性。

7 结语

近年来越来越重视干线运输及城市轨道交通中列车车辆控制系统可靠性及安全性的研究。车载计算机作为车辆微机控制系统中的重要环节,其自身安全性及可靠性至关重要。本文从硬件和软件2个方向,介绍了一种车载计算机的高可靠性研究及设计方案,讨论了一些主要问题,探讨冗余容错的硬件实现技术方法以及软件系统特点。工程人员在研究设计列车车辆控制系统时,始终需要把安全放在重要位置,以确保车辆控制系统稳定运行。

[1] 唐涛,郜春海,张方,等.高速铁路列车运行控制系统车载设备安全性设计[J].北方交通大学学报,1999,23(5):83.

[2] 张利芬,袁普及.嵌入式冗余计算机的设计与实现[J].计算机工程,2009,35(2):230.

[3] 李小康,高荣芳,陈江.VxWorks启动过程解析[J].中国科技信息,2008(21):94.