基于单片机与CPLD的无线控制系统

张九宾 张丕状 杜坤坤

摘 要:介绍一种基于单片机与CPLD结合的传感器网络节点的无线控制系统。节点中单片机对无线命令进行译码,并对外围子模块进行控制,CPLD扩展控制系统的并行I/O端口、SPI串行接口等,从而根据系统需要可扩展无线传感网络节点的外围功能模块。采用单片机与CPLD模块化设计方法,降低了设计成本,方便电路的多次改进,为传感器网络节点在不同场合的应用提供了一种通用的方法。

关键词:单片机I/O端口扩展;CPLD;控制节点;SPI串行接口扩展

中图分类号:TP302.1 文献标识码:B

文章编号:1004-373X(2009)01-094-03

Wireless Control System Based on Single Chip Computer and CPLD

ZHANG Jiubin,ZHANG Pizhuang,DU Kunkun

(School of Information and Communication Engineering,North University of China,Taiyuan,030051,China)

Abstract:

A wireless control system of sensor network nodes with the combination of single chip computer and CPLD is introduced.In the node,single chip computer decodes the wireless commands and controls expansion modules,CPLD expands control system parallel I/O ports and serial SPI ports,the system can expand periphery function modules according to need.The way of module design with the combination of single chip computer and CPLD can low cost price,facilitate the circuit several times to improve and provide a common method for the sensor network nodes in the application of different occasions.

Keywords:single chip computer I/O expansion;CPLD;control node;SPI serial interface expansion

0 引 言

自单片机引入我国以来,相关产品的普及促使单片机的应用设计日益广泛。传统的单片机控制系统由单片机以及外围扩展芯片组成,但是这些外围芯片一般具有接线重复性高、体积大等缺点。可编程逻辑宏单元或逻辑块之间的相互连线在同一封装内,受外界干扰影响小,电磁兼容(EMC)性能好。对设计者来说,CPLD器件最大的优点在于可现场编程,改变逻辑关系时,无需更改外部线路板,只需用图形语言程序或硬件描述语言程序来改变电路,生成下载编辑软件,通过下载电缆输入CPLD器件即可,非常方便,特别有利于新品试制,大大缩短了开发周期。使用CPLD和单片机结合构成其外围电路可以减少系统芯片数量,缩小系统体积,提高系统可

靠性。

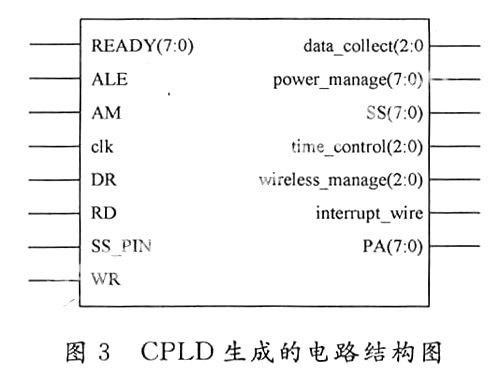

1 控制系统

该系统是一个无线传感器网络节点的控制系统,它用于控制无线模块接收主站发送过来的信息,单片机读取这些数据并译码后,根据译码结果控制各功能子模块,如无线模块控制、温度采集控制、电源管理控制、时间统一信号控制等功能,共需要28个输出控制 I/O口,13个输入控制I/O口,扩展I/O端口分配 8个。各外围模块通过SPI串行标准接口的扩展与单片机和CPLD进行通信,并完成数据传输控制功能。各外围模块只需接受MCU的控制命令,即可独立完成外围模块各自的功能:无线模块的收发、数据采集A/D转换、时间统一记录、电源管理等。同时预留单片机通过 USART的串口输出,另外,还需要此系统具有很好的扩展性,通过扩展外围模块来增加节点不同的功能。系统设计要求如图1所示。

根据设计要求,单片机系统要8 b的UART串行输出以及SPI串行输入输出,同时为了完成各种控制功能,单片机必须至少扩展7个I/O端口。如果使用传统的扩展方法,在输出速率要求不高的情况下,并行接口通常使用8255传统的微处理器接口芯片来扩展。

但是,这些芯片都是40脚DIP封装,体积庞大,并且每片最多只能扩展3个8 b I/O端口,还要考虑8255中A,B,C口是作为输入口还是输出口。当需要的控制端口较多时,不得不用多个这种专用芯片。这时需重复连接多片8255的8位数据线、单片机读/写信号线、ALE,CS(片选)和A0,A1信号线,增加了单片机硬件、软件的设计难度,也就造成电路复杂、控制不便、可靠性降低,而且增大了电路的功耗、体积和重量。同时接口芯片提供的端口数未必与实际需要的端口数相等,不能根据实际情况分配I/O端口的数量,容易造成芯片部分资源的浪费。而CPLD具有丰富的可编程I/O引脚,并且由于其在系统可编程的特点,设计者能够自己定义器件的内部逻辑和管脚,扩展电路也具有可编程设计的特点,方便电路的多次改进,降低了设计成本。

2 单片机与CPLD

AVR单片机,采用精简指令集CPU(RISC),具有高性能,处理速度快(1 MIPS/MHz),成本低,包括FLASH程序存储器、看门狗、E2PROM、同/异步串口、SPI 、ADC、 定时器/计数器,众多的中断系统,集成多种功能,具有低功耗抗干扰的休眠模式。

复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)是一种半定制的专用集成电路(Application Specific Integrated Circuit,ASIC)。其芯片上按一定排列方式集成了大量的门和触发器等基本逻辑元件。通过软件编程可以实现这些元件的连接,从而使之完成某个逻辑电路或系统的功能,成为一个可在实际电子系统中使用的ASIC。

目前,最大的两家CPLD/FPGA生产厂商分别是ALTERA 以及Xilinx。该系统使用的Xilinx的XC2C256属于Xilinx公司的Coolrunner2系列,包含256个宏单元,最大用户I/O管脚有100个。

3 系统硬件连接组成以及工作过程

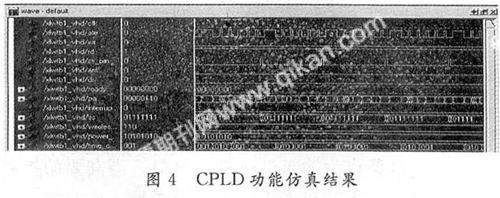

使用CPLD代替单片机的外围接口芯片,与AVR单片机构成的控制系统相连如图2所示。系统的主要部分仅需要2片集成电路,AVR单片机系列ATmega162和XC2C256。单片机与CPLD之间的接口是通过单片机的地址/数据复用总线(PORTA端口)以及读写控制I/O口(WR,RD,ALE)与CPLD的I/O口相连来进行数据、状态的传输。

在单片机中对扩展的I/O端口进行统一编址,通过C语言可以方便地访问I/O端口,单片机要往数据端口或控制端口输出信息,必须先把地址送到地址总线上,将确定的控制信息送到控制总线上,再把数据信息送到数据总线上。经过CPLD的内部逻辑进行地址、数据锁存,并译码以获得扩展的端口号,从而获得对各个外部功能子模块的控制信号,端口号COM

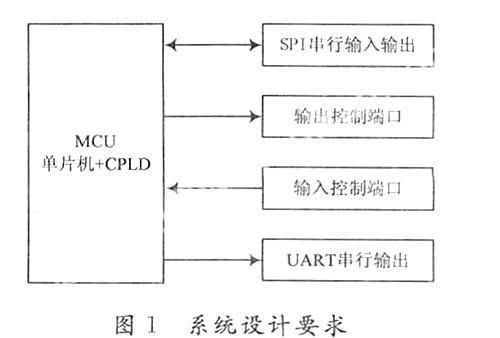

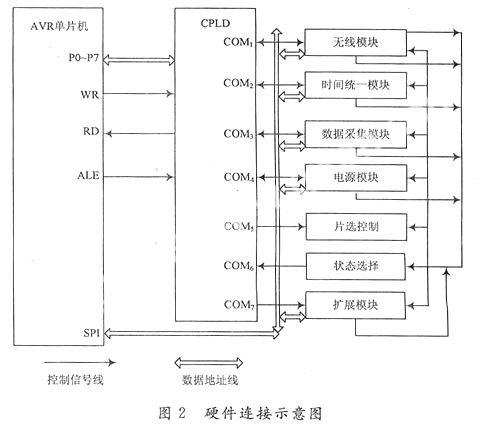

通过选择不同的I/O端口可以控制读取、写入各外围处理模块的数据。要读取某一外围处理模块的数据,必须先读取状态选择端口COM 4 CPLD软件设计 采用Xilinx公司的CPLD开发软件Xilinx ISE完成系统的软件设计,Xilinx ISE支持原理图输入、HDL语言输入、状态图输入和混合输入等输入方法。其中HDL语言中的VHDL硬件描述语言,与具体的工艺技术和器件无关,易于共享和复用,具有多层次描述系统硬件功能的能力。 在设计中,CPLD需要实现的功能为地址译码端口以及控制不同端口的电路设计,用VHDL语言对进行编程编译,然后采用元件例化的方法得到电路结构如 图3所示。 CPLD中所设计的程序片断: addr_code<=RD≀&PA;_i_latch; 地址译码功能电路 p2: process(addr_code) begin case addr_code is when″100000″=>adrr_cs<=″111111111110″; --cs(0),电源管理 when ″100001″=>adrr_cs<=″111111111101″; --cs(1),时间统一模块控制端口 when ″100010″=>adrr_cs<=″111111111011″; --cs(2),无线模块模式控制端口 when ″100011″=>adrr_cs<=″111111110111″; --cs(3),数据采集模块控制端口 when ″100100″=>adrr_cs<=″111111101111″; --cs(4),片选选择端口 when ″100101″=>adrr_cs<=″111111011111″; --cs(5),状态端口 when others =>adrr_cs<=″111111111111″; end case; end process p2;--无线模块模式控制电路 p: process(adrr_cs(2),PA_i(2 downto 0)) begin if (adrr_cs(2)′event and adrr_cs(2) = ′0′)then wireless_manage<=PA_i(2 downto 0); end if; end process p;--片选不同的功能模块通过扩展SPI与单片机通信 p:process(SS_PIN,adrr_cs(4),PA_i(2 downto 0),csaddr) begin if (adrr_cs(4)′event and adrr_cs(4) = ′0′)then csaddr<=PA_i(2 downto 0); end if; if (SS_PIN=′0′) then case csaddr is when ″000″ => SS <=″11111110″; when ″001″ => SS <=″11111101″; when ″010″ => SS <=″11111011″; when others => SS<=″11111111″; end case; else SS<=″11111111″; end if; end process p; 地址译码端口以及不同端口实现的功能仿真结果如图4所示。可以看出,仿真结果符合设计要求。 5 单片机软件设计 AVR单片机固化程序采用ICC语言编写,并使用模块化的设计方法,分为初始化程序、预定义子程序、主程序、无线收发控制程序、各功能模块控制程序、读功能子模块的子程序、配置功能子模块程序、超时程序等。模块化设计使软件更加灵活,便于调用和移植,并且在错误发生的时候,可以很快找到错误,极大地提高了系统的可靠性和稳定性。 单片机中要对扩展的不同I/O端口分配相对应的不同的内存地址。例如:要对扩展的电源管理I/O端口分配单片机所映射的内存地址为Ox2000。可以写成:#define POWER_ADDR (*( unsigned char *)0x2000)。 单片机主要完成系统的控制功能,在实现输出控制接口时需要与CPLD配合,提供CPLD需要的数据和地址及控制线。当需要某一组输出工作时,在单片机中用C语言对宏变量对应的地址进行赋值,“WR”或“RD” 同时就被拉低,CPLD通过这组信号判断选择并且使能某一组输出工作,并将输出控制代码从单片机经过CPLD的相应端口输出,完成控制功能。例如对电源管理单片机中定义的I/O端口对应的内存地址为:#define POWER_ADDR (*(unsigned char *)0x2000),当用C语言写下POWER_ADDR=0x12时,就会在CPLD的8个I/O口输出相应的控制信息“00010010”,从而对各功能模块进行供电或断电。 6 结 语 采用CPLD作为单片机I/O端口的扩展芯片,大大减少了单片机外围所用芯片的种类和数量,缩小了体积,降低了功耗,提高了系统的可靠性和整体性。使用单片机和CPLD结合可以有效地实现过去需要利用单片机和大量外围接口芯片才能完成的功能,而且还可以根据需要不断地扩展外围电路,只需要修改CPLD的程序就可以实现用户的需求。CPLD器件与单片机结合,可以优势互补,组成灵活的、硬软件都可现场编程的控制器,缩短开发周期,适应市场需要。 参考文献 [1]李彬,萧德云,张正芳.基于单片机和CPLD的智能I/O模块设计.计算机工程与应用,2006,42(36):66-69. [2]何立民.单片机高级教程——应用与设计.北京:北京航空航天大学出版社,2003. [3]赵鑫,蒋亮,齐兆群,等.VHDL与数字电路设计.北京:机械工业出版社,2005. [4]罗苑棠.CPLD/FPGA常用模块与综合系统设计实例精讲.北京:电子工业出版社,2007. [5]李庆,亓科,于敬芬.基于CPLD与单片机的多路高精度数据采集系统设计.海军工程大学学报,2007,19(3): 62-65. [6]沈周义,许克滨.采用CPLD增强单片机P89C669外部设备扩展能力.现代电子技术,2007,30(13):63-65. [7]程耕国,刘涛.CPLD扩展51单片机寻址范围.微计算机信息,2006,22(5Z):185-186,10. [8]蔡锦元.CPLD器件在单片机控制器中的使用.现代电子技术,2006,29(22):1-3. [9]沈文,Eagle lee,詹卫前.AVR单片机C语言开发入门指导.北京:清华大学出版社,2007. [10]杨美刚,李小文.SPI接口及其在数据交换中的应用.通信技术,2007(11):385-387. 作者简介张九宾 男,1981年出生,山西运城人,现就读于中北大学信息与通信工程学院,硕士研究生。 张丕状 男,1965年出生,教授,博士,硕士生导师。中北大学信息与通信工程学院信息工程系副主任,中北大学山西省无损检测中心青年骨干。主要从事信号信息处理、数据采集测试工作。 杜坤坤 女,1983年出生,山东聊城人,现就读于中北大学信息与通信工程学院,硕士研究生。